|

Главная |

Структурная схема процессора семейства ADSP-2100

|

из

5.00

|

|

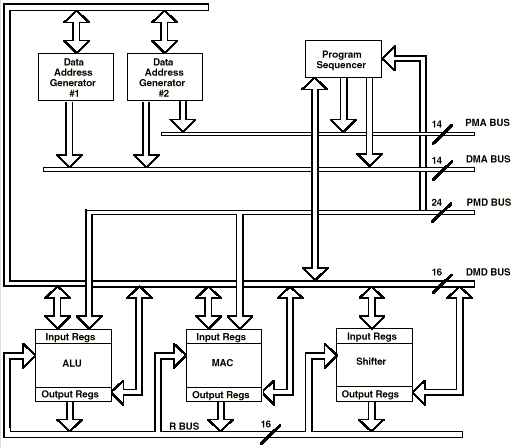

Как уже говорилось выше каждый процессор содержит три независимых вычислительных модуля:

- арифметико-логический (ALU);

- умножение с накоплением (MAC);

- расширитель (shiffter).

Эти устройства работают с 16-разрядными данными и обеспечивают аппаратную поддержку мультиточности.

ALU выполняет ряд стандартных арифметических и логических команд в дополнение к примитивам деления. MAC выполняет одно-цикловые операции умножения, умножения/сложения, умножения/вычитания. Shiffter осуществляет логические и арифметические сдвиги, нормализацию, де нормализацию и операцию получения порядка, атак же управление форматом данных, разрешая работу с плавающей точкой. Вычислительные модули размещаются последовательно друг за другом, таким образом чтобы выход одного мог стать входом другого в следующем цикле. Результаты работы модулей собираются на 16-разрядную R-шину.

Все три модуля содержат входные и выходные регистры, которые доступны через 16-разрядную DMD-шину. Команда, выполняемые в модулях, берут в качестве операндов данные находящиеся в регистрах ввода и после выполнения записывают результат в регистры вывода. Регистры являются как бы промежуточным хранилищем между памятью и вычислительной схемой. R-шина позволяет результату одного вычисления стать операндом к другой операции. Это позволяет сэкономить время обходясь без лишних пересылок модуль-память.

Генераторы адресов данных и программа sequencer

Два специализированных генератора адресов данных (DAGs) и мощная программа sequencer гарантируют эффективное использование вычислительных модулей. DAGs обеспечивают адреса памяти, когда необходимо поместить данные из памяти в регистры ввода вычислительных модулей, либо сохранить в результат из выхоных регистров. Каждый DAG отвечает за четыре указателя адреса. Если указатель используется для косвенной адресации то измениятся значение некоторого регистра. С двумя генераторами процессор может выдавать два адреса одновременно для выборки из памяти двух операндов.

Для автоматической адресации модуля круговых буферов значение длины операнда может быть связано с каждым указателем. (Круговая буферная особенность также используется последовательными портами для автоматической передачи данных).

DAG1 обеспечивает адреса только для данных, DAG2 – для данных и программ. Когда в регистре состояния (MSTAT) установлен соответствующий бит режима, адрес вывода DAG1 прежде чем попасть на шину адреса инвертируется. Эта особенность облегчает работу в двоичной системе.

Программа Sequenсer обеспечивает последовательность команд и адресацию памяти программы. Sequencer управляется регистром команд, который указывает на команду, которая в данный момент выполняется. Выбранные команды записываются в регистр команд за один такт процессора и выполняются в течении следующего. Чтобы уменьшить количество циклов, sequencer поддерживает работу с условными переходами.

Шины

Процессоры семейства имеют пять внутренних шин. Шины адреса программы (PMA) и адреса данных (DMA) связаны с адресами памяти данных и программы. Шина данных программы (PMD) и шина данных (DMD) используются для передачи информации связанной с областями памяти. Шины мультиплексированы в одну внешнюю шину адреса и одну внешнюю шину данных. R-шина предназначена для передачи промежуточных результатов непосредственно между вычислительными модулями.

Адресная шина PMA шириной 14 бит обеспечивает достум к 16Кбайтам смешанной системы команд и данных. 24-разрядная шина PMD предназначена для работы с 24-битными командами.

Адресная шина DMA шириной 14 бит, обеспечивает прямой доступ к 16Кбайтам области данных. 16-разрядная шина DMD предназначена для внутренних пересылок между любыми регистрами процессора и регистров с памятью в одиночном цикле. Адрес памяти данных исходит из двух источников: абсолютное значение, определенное в системе команд (прямая адресация) или вывод данных адресует генератор (косвенная адресация). Воспользоваться данными из области команд можно лишь с помощью косвенной адресации.

Шина данных памяти программы (PMD) предназначена для передачи данных в вычислительные модули и считывания результата вычислений через PMD-DMD модуль обмена. Этот модуль позволяет передавать данные от одной шины к другой. Он имеет аппаратные средства для перехода от 8-разрядной шины к другой.

|

из

5.00

|

Обсуждение в статье: Структурная схема процессора семейства ADSP-2100 |

|

Обсуждений еще не было, будьте первым... ↓↓↓ |

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы